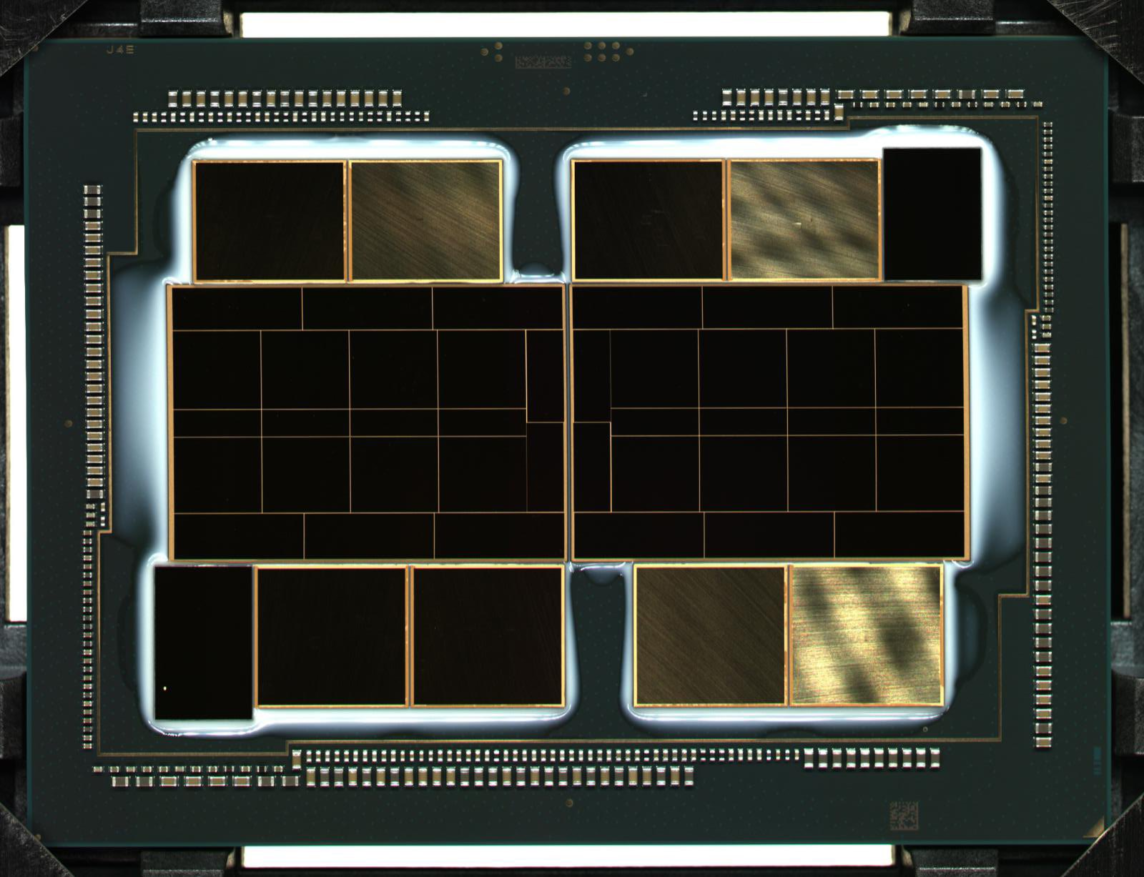

В прошлом году Intel подтвердила, что Xe-HPC основан на технологии упаковки Foveros CO-EMIB, поскольку сам процессор состоит из нескольких микросхем, изготовленных с использованием разных узлов.

Базовая плитка изготавливается с использованием 10-нанометровой архитектуры Intel SuperFin, но, например, Rambo Cache Tile уже использует 10-нанометровую архитектуру в Enhanced SuperFin. Вычислительная плитка изготавливается с использованием внешних узлов и узлов Next-Gen, в то время как плитка ввода-вывода Xe изготавливается исключительно с использованием внешнего литейного производства.

Предполагается, что графический процессор Xe-HPC имеет 8 вычислительных ядер на двух плитках, но в настоящее время неизвестно, сколько исполнительных единиц вмещает каждая плитка. На прошлой официальной фотографии — четыре стопки HBM для каждой из двух матриц.

Xe-HPC готов к включению, это значит, что чип уже активирован в лаборатории Intel и в настоящее время проходит тестирование. Ожидается, что Intel Xe-HPC дебютирует с процессорами Xeon нового поколения на архитектуре Sapphire Rapids.

Читать еще:

Ядерный ракетный двигатель строят для полетов на Марс. Чем он опасен?

Посмотрите на изображение Марса из 8 триллионов пикселей.

Лунная пыль смертельно опасна для человека. Спутник Земли не подходит для колонизации?

Аборты и наука: что будет с детьми, которых родят.